Chapter 4. CPU의 작동원리

04-1. ALU와 제어장치

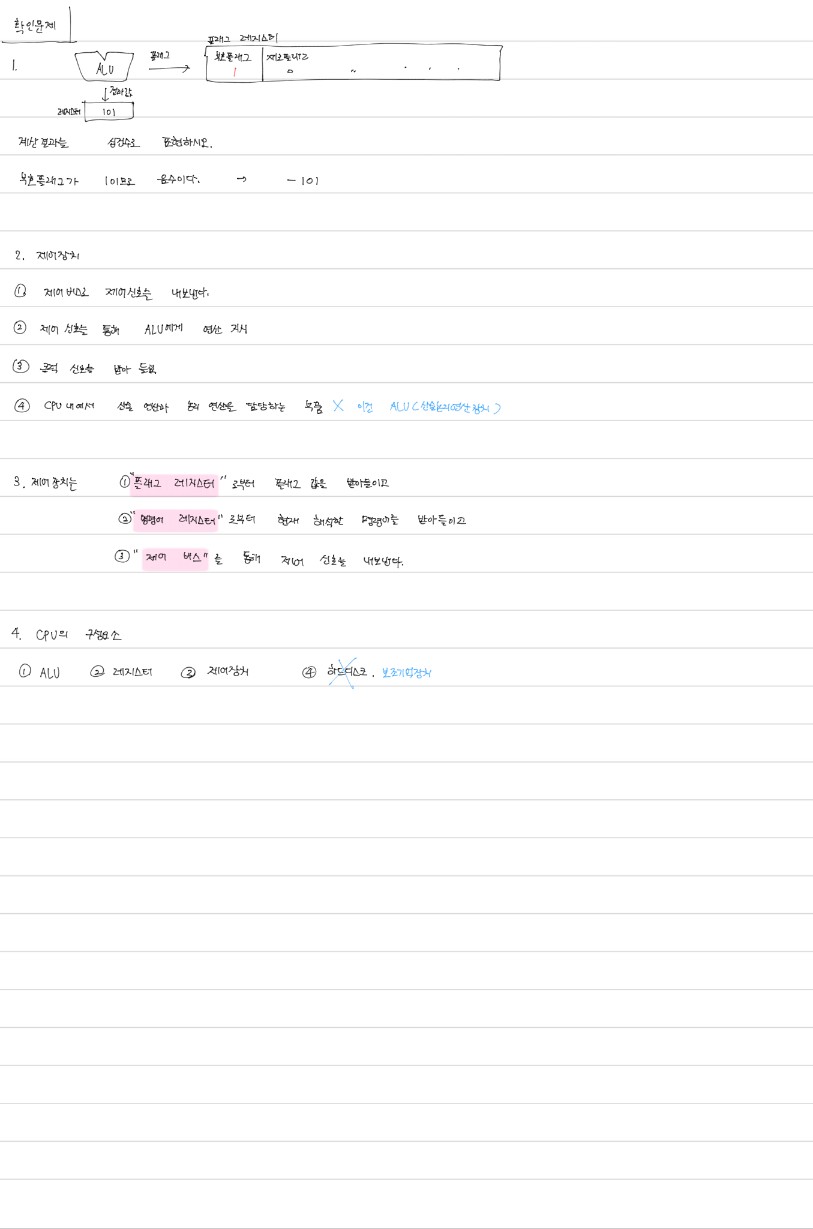

ALU는 레지스터로부터 피연산자를 받아들이고, 제어장치로부터 제어 신호를 받아들인다.

ALU는 연산 결과와 플래그를 내보낸다.

제어장치는 클럭, 현재 수행할 명령어, 플래그, 제어 신호를 받아들인다.

제어장치는 CPU 내부와 외부로 제어 신호를 내보낸다.

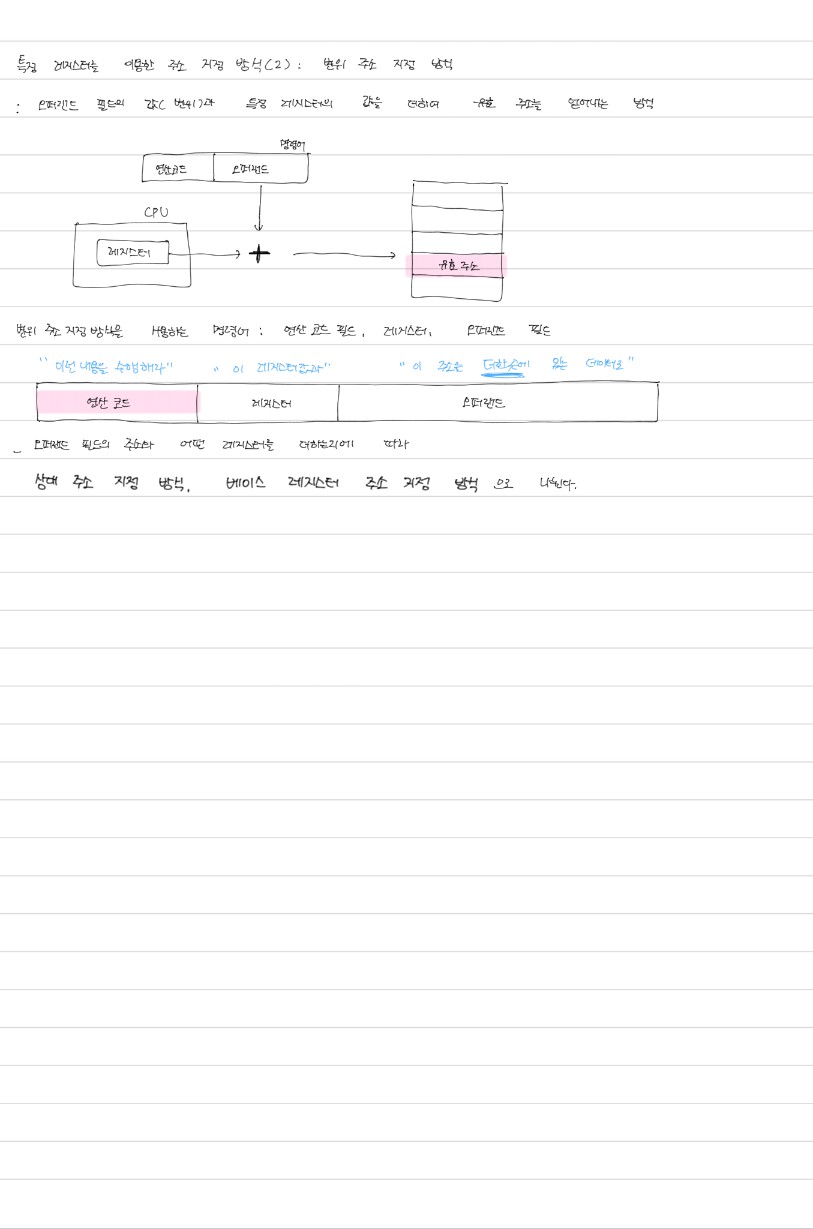

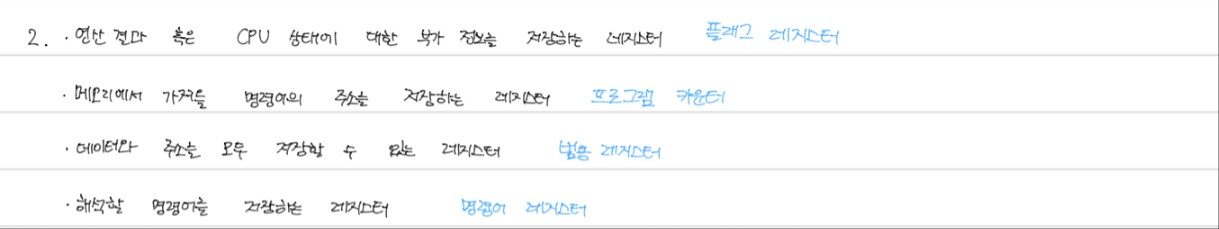

04-2. 레지스터

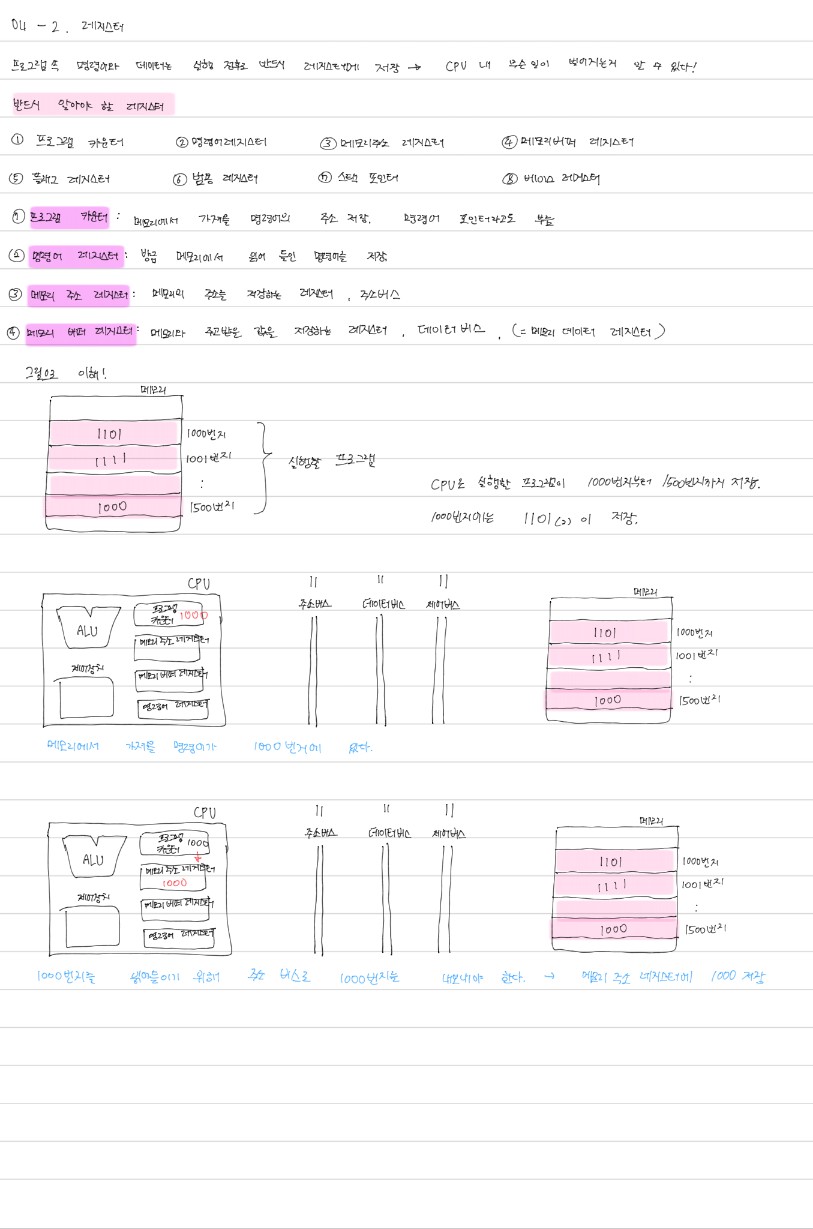

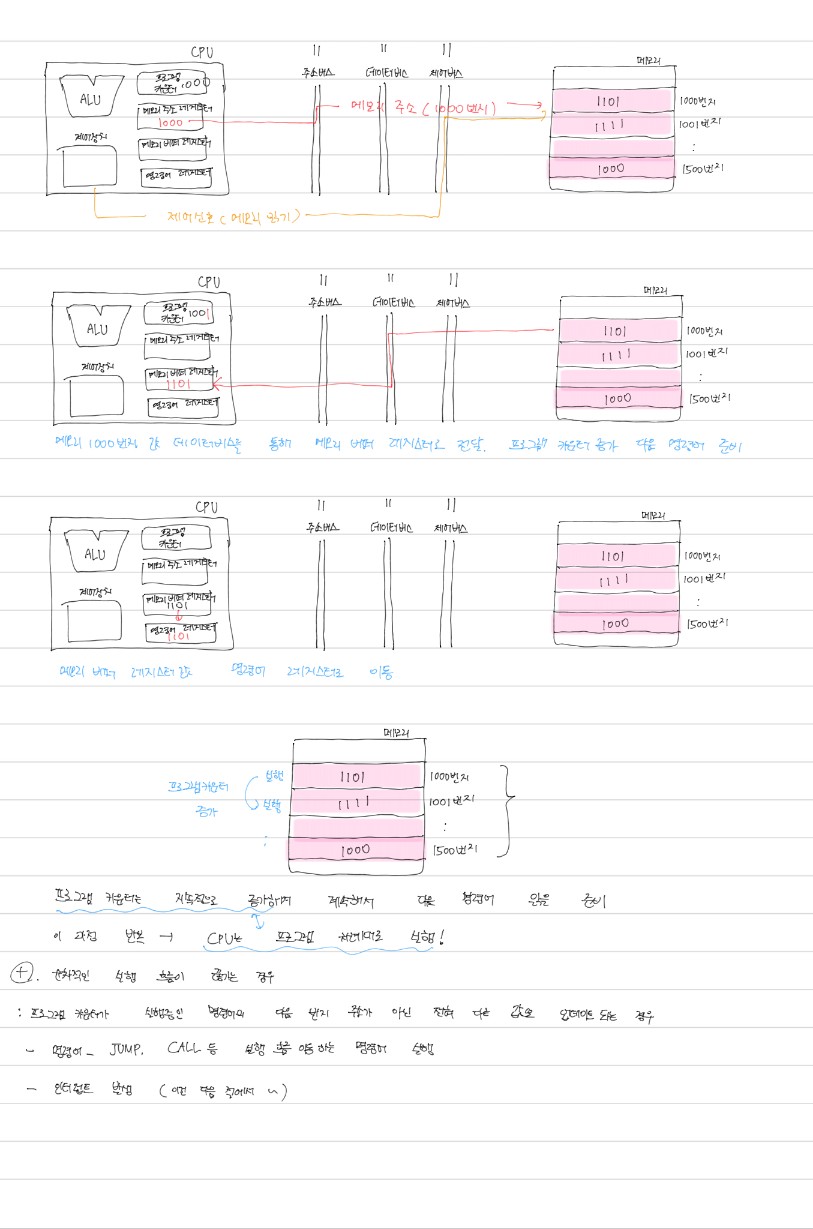

프로그램 카운터는 메모리에서 가져올 명령어의 주소, 명령어 레지스터는 해석할 명령어를 저장한다.

메모리 주소 레지스터는 메모리 주소, 메모리 버퍼 레지스터는 메모리와 주고받을 데이터를 저장한다.

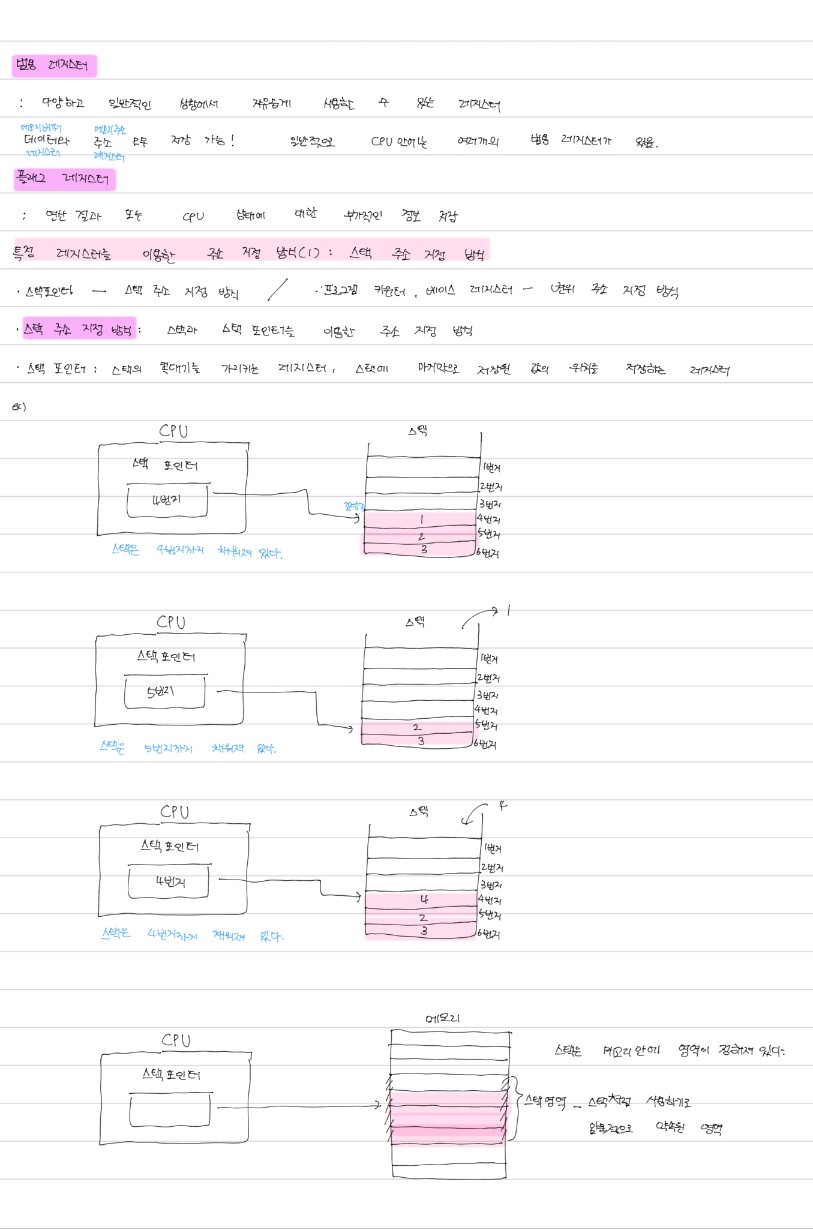

범용 레지스터는 데이터와 주소 모두 저장하고, 플래그 레지스터는 연산 결과 혹은 CPU 상태에 대한 부가 정보를 저장한다.

스택 포인터는 스택 최상단의 위치를 저장한다.

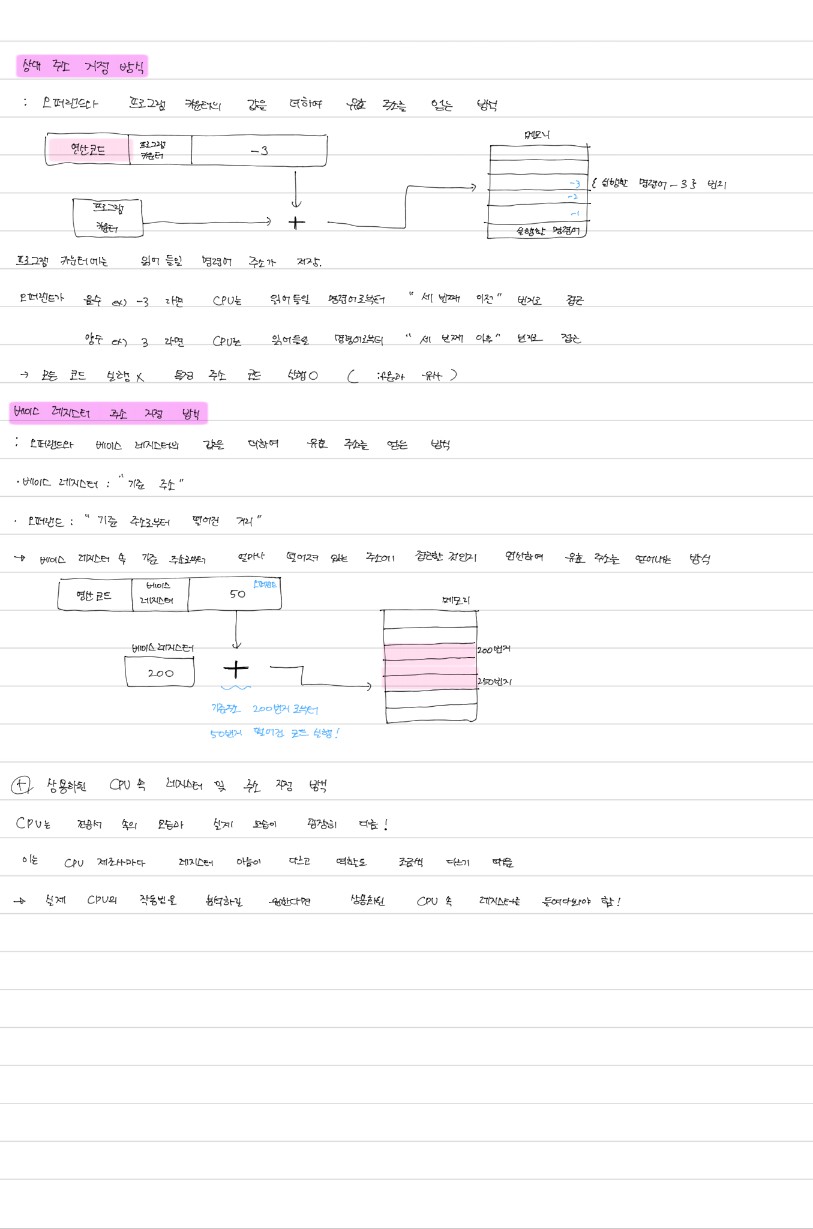

베이스 레지스터에 저장된 주소는 기준 주소로서의 역할을 한다.

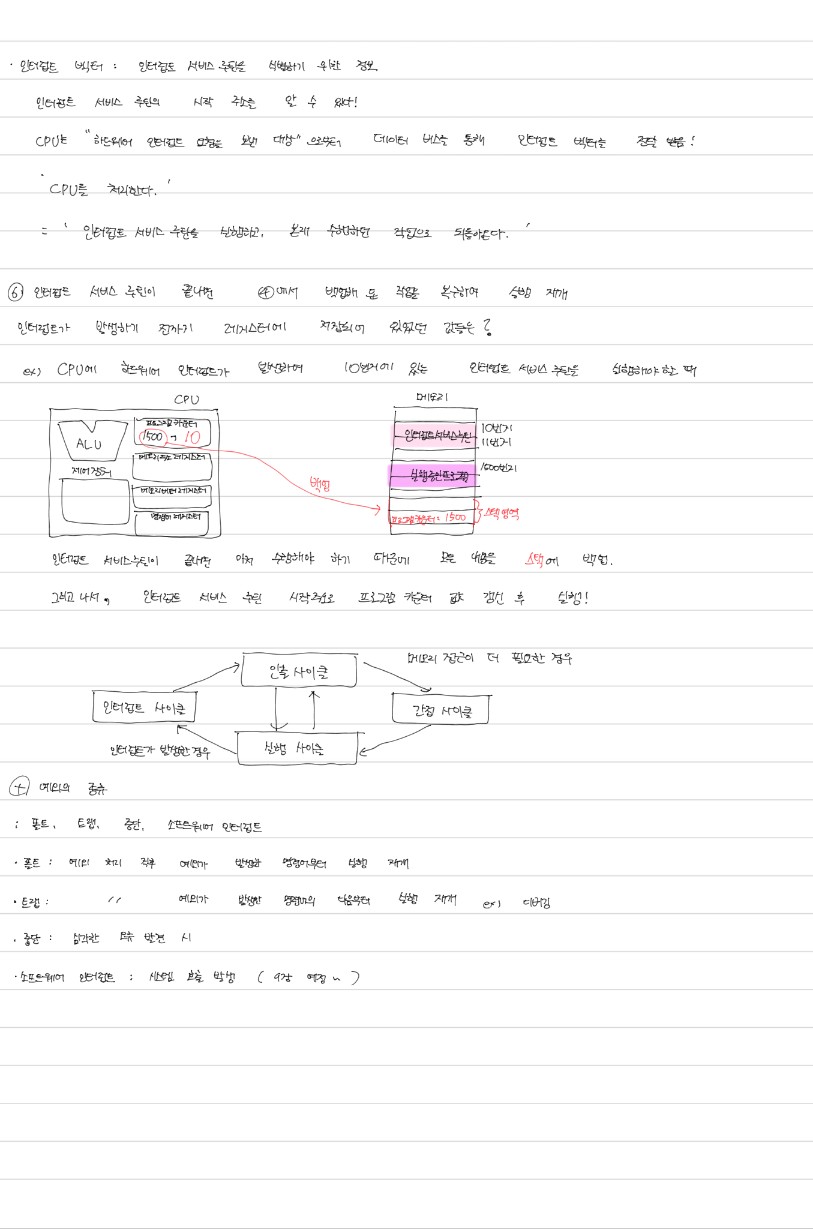

04-3. 명령어 사이클과 인터럽트

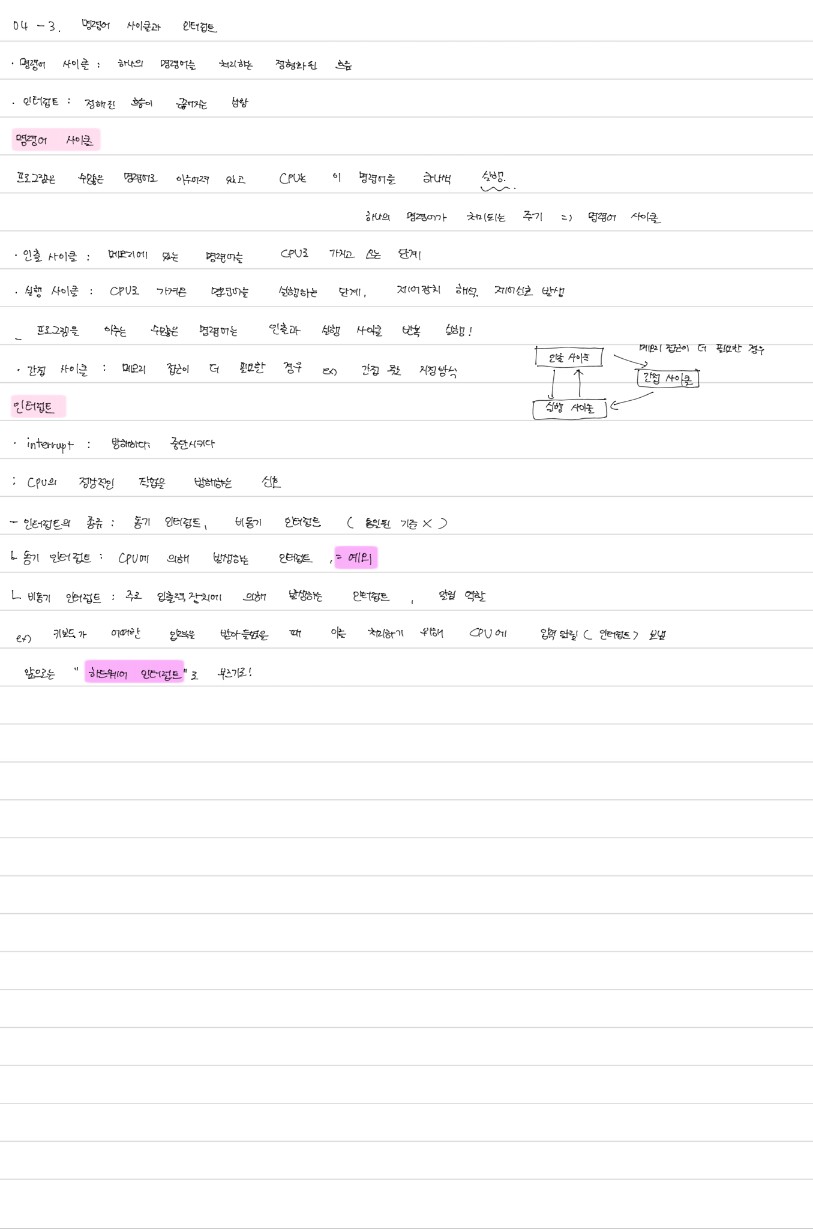

명령어 사이클은 하나의 명령어가 처리되는 주기로 인출, 실행, 간접, 인터럽트 사이클로 구성된다.

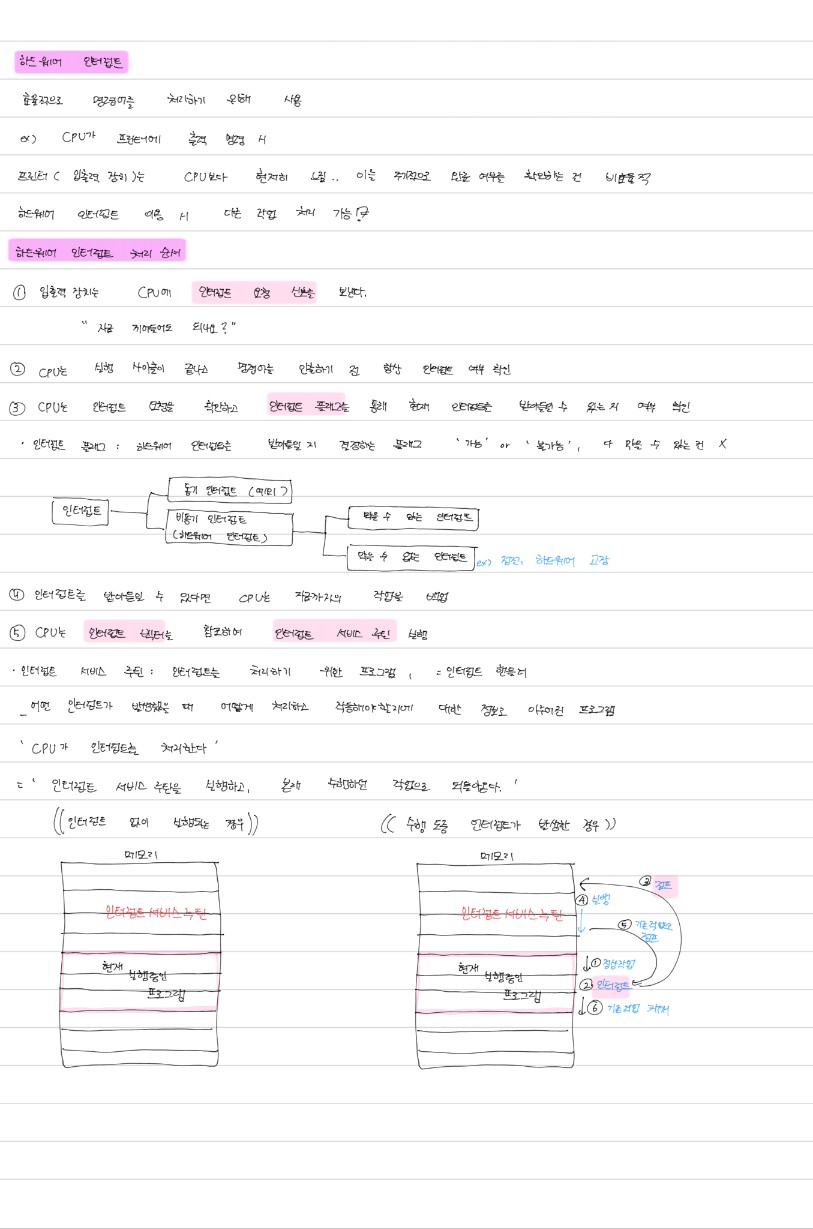

인터럽트는CPU의 정상적인 작업을 방해하는 신호다.

인터럽트의 종류에는 예외와 하드웨어 인터럽트가 있다.

인터럽트 서비스 루틴은 인터럽트를 처리하기 위한 동작들로 이루어진 프로그램이다.

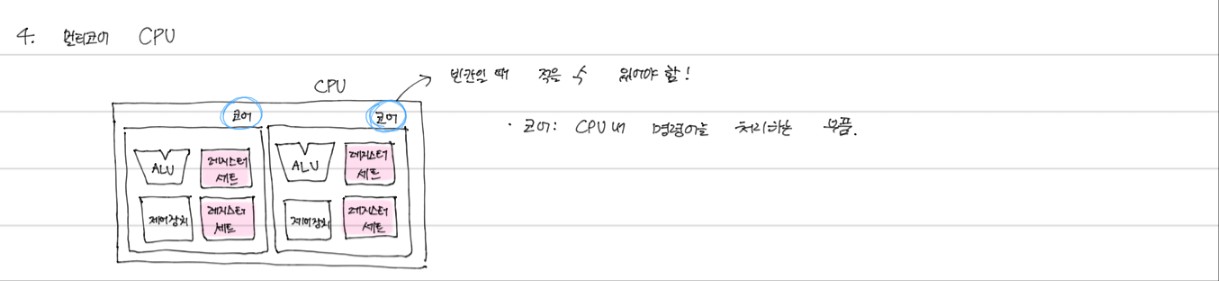

Chapter 5. CPU 성능 향상 기법

05-1. 빠른 CPU를 위한 설계 기법

클럭속도가 높은 CPU는 빠르게 작동한다.

코어란 CPU 내에서 명령어를 실행하는 부품이다.

멀티코어 프로세서란 여러 개의 코어를 포함하는 CPU이다.

스레드에는 하드웨어적 스레드와 소프트웨어적 스레드가 있다.

멀티스레드 프로세서란 하나의 코어로 여러 개의 명령어를 동시에 실행할 수 있는 CPU를 말한다.

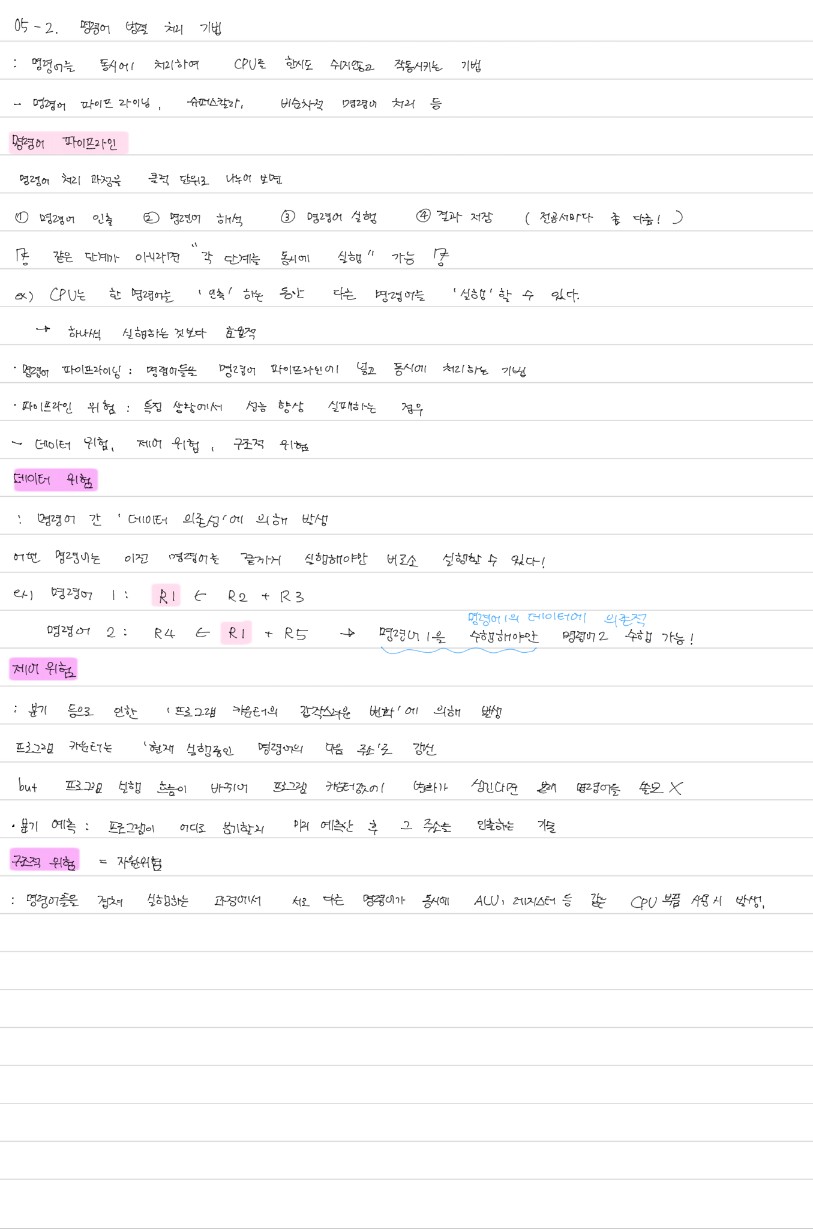

05-2. 명령어 병렬 처리 기법

명령어 파이프라이닝은 동시에 여러 개의 명령어를 겹쳐 실행하는 기법이다.

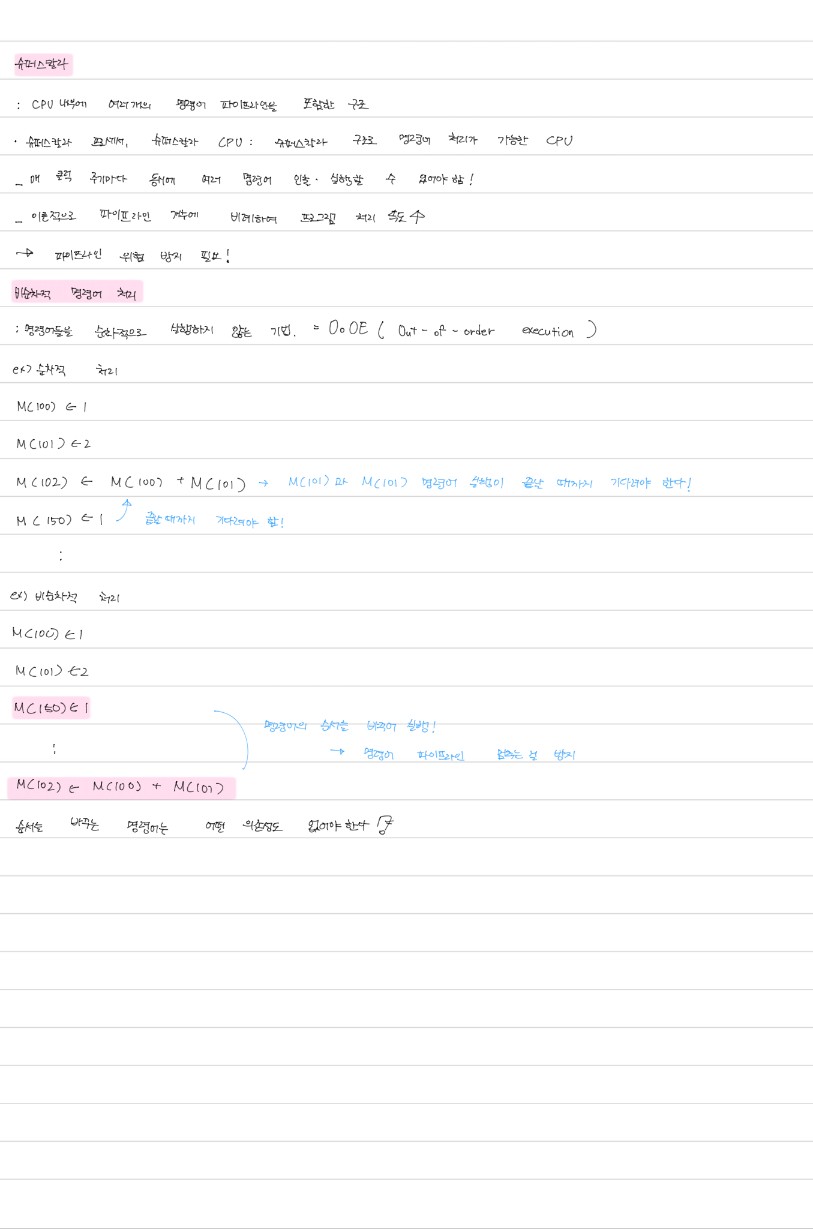

슈퍼스칼라는 여러 개의 명령어 파이프라인을 두는 기법이다.

비순차적 명령어 처리 기법은 파이프라인의 중단을 방지하기 위해 명령어를 순차적으로 처리하지 않는 기법이다.

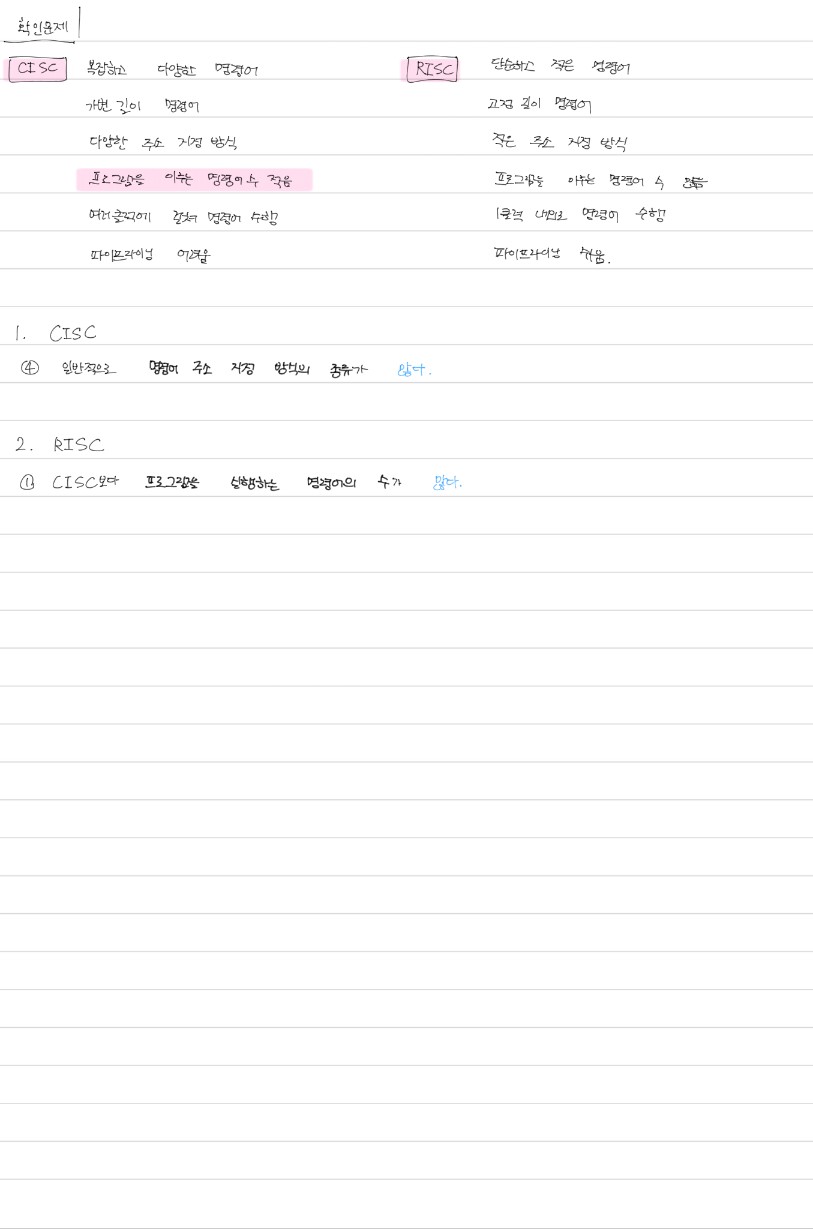

05-3. CISC와 RISC

ISA는 CPU의 언어이자 하드웨어가 소프트웨어를 어떻게 이해할지에 대한 약속이다.

CISC는 복잡하고 다양한 종류의 가변 길이 명령어 집합을 활용한다.

RISC는 단순하고 적은 종류의 고정 길이 명령어 집합을 활용한다.

4장 공부기록

5장 공부기록

미션1

미션2

선택미션. 코어와 스레드, 멀티코어와 멀티 스레드 개념 정리

코어: CPU 내에서 명령어를 실행하는 하드웨어 부품

스레드: 실행 흐름의 단위, 하드웨어적 스레드와 소프트웨어적 스레드가 있음

멀티코어 프로세서: 명령어를 실행할 수 있는 하드웨어 부품이 CPU 안에 두 개 이상 있는 CPU

멀티스레드 프로세서: 하나의 코어로 여러 개의 명령어를 동시에 실행할 수 있는 CPU, 하드웨어 스레드

여행갔다오고 여운이 길게 남아 정신못차리다가 지각했다 ...ㅠㅠㅠㅠㅠ

밀린 학습량보고 애써 외면했는데 막상 하면 되니까!!

이미 지나간 시간을 돌릴 순 없으니 이번주부터 정상제출을 목표로 다시 열심히 달리자!!

'컴퓨터구조' 카테고리의 다른 글

| [혼공학습단 11기] #1. Ch 1 ~ Ch 3 (1) | 2024.01.05 |

|---|